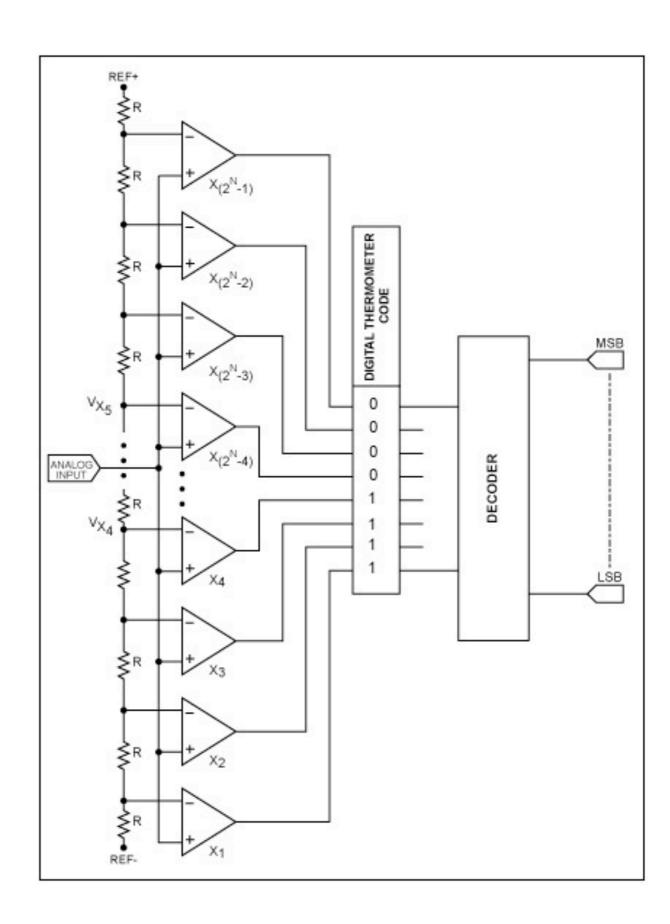

### **Flash**

cascade of n comparators fastest (Gsps)

low resolution (n ~ 8)

more expensive

### **Flash**

cascade of n comparators fastest (Gsps)

low resolution (n ~ 8)

more expensive

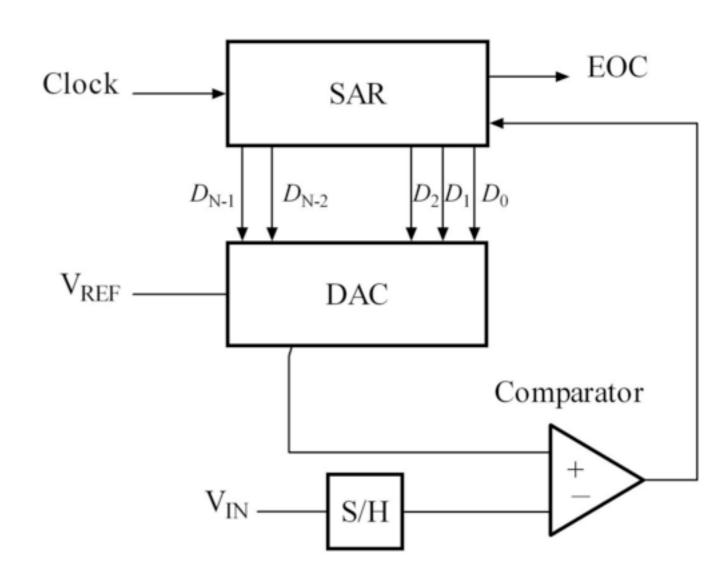

### **Successive Approximation**

compares input to internal DAC starts with MSB successively updates DAC to match mid-range speed (Msps)

### **Flash**

cascade of n comparators fastest (Gsps)

low resolution (n ~ 8)

more expensive

### **Successive Approximation**

compares input to internal DAC starts with MSB successively updates DAC to match mid-range speed (Msps)

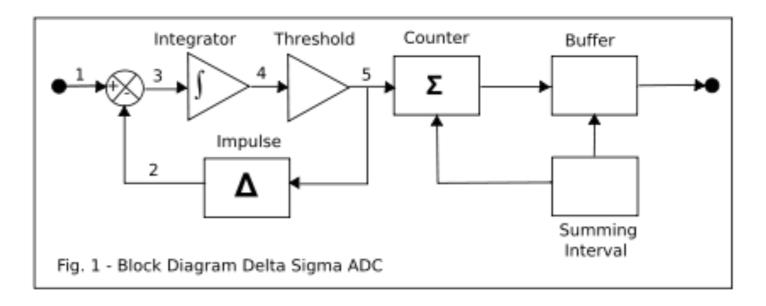

### Sigma-Delta

oversamples then filters highest possible resolution lower-speed (<Msps)

### **Flash**

cascade of n comparators fastest (Gsps)

low resolution (n ~ 8)

more expensive

### **Successive Approximation**

compares input to internal DAC starts with MSB successively updates DAC to match mid-range speed (Msps)

### Sigma-Delta

oversamples then filters highest possible resolution lower-speed (<Msps)

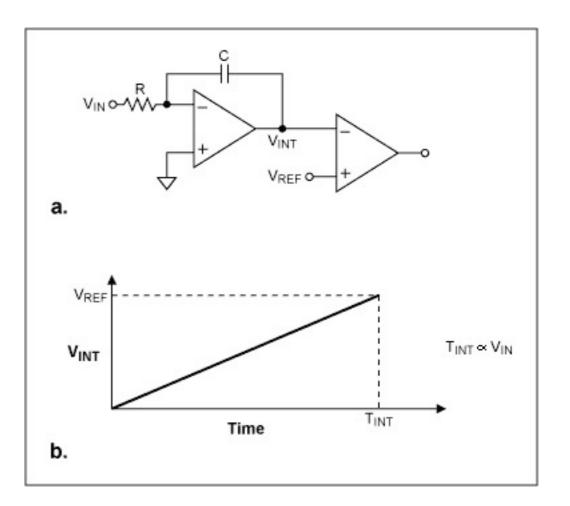

### **Integrating**

compares against ramp reference counts time until compare lowest-speed (<100ksps)

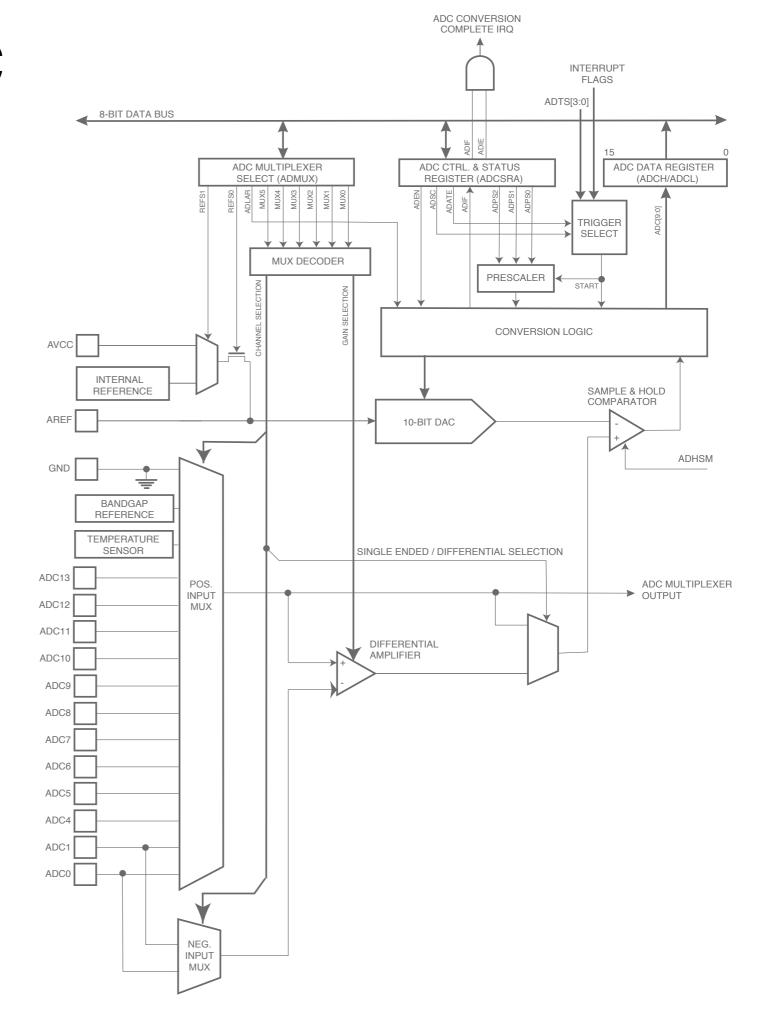

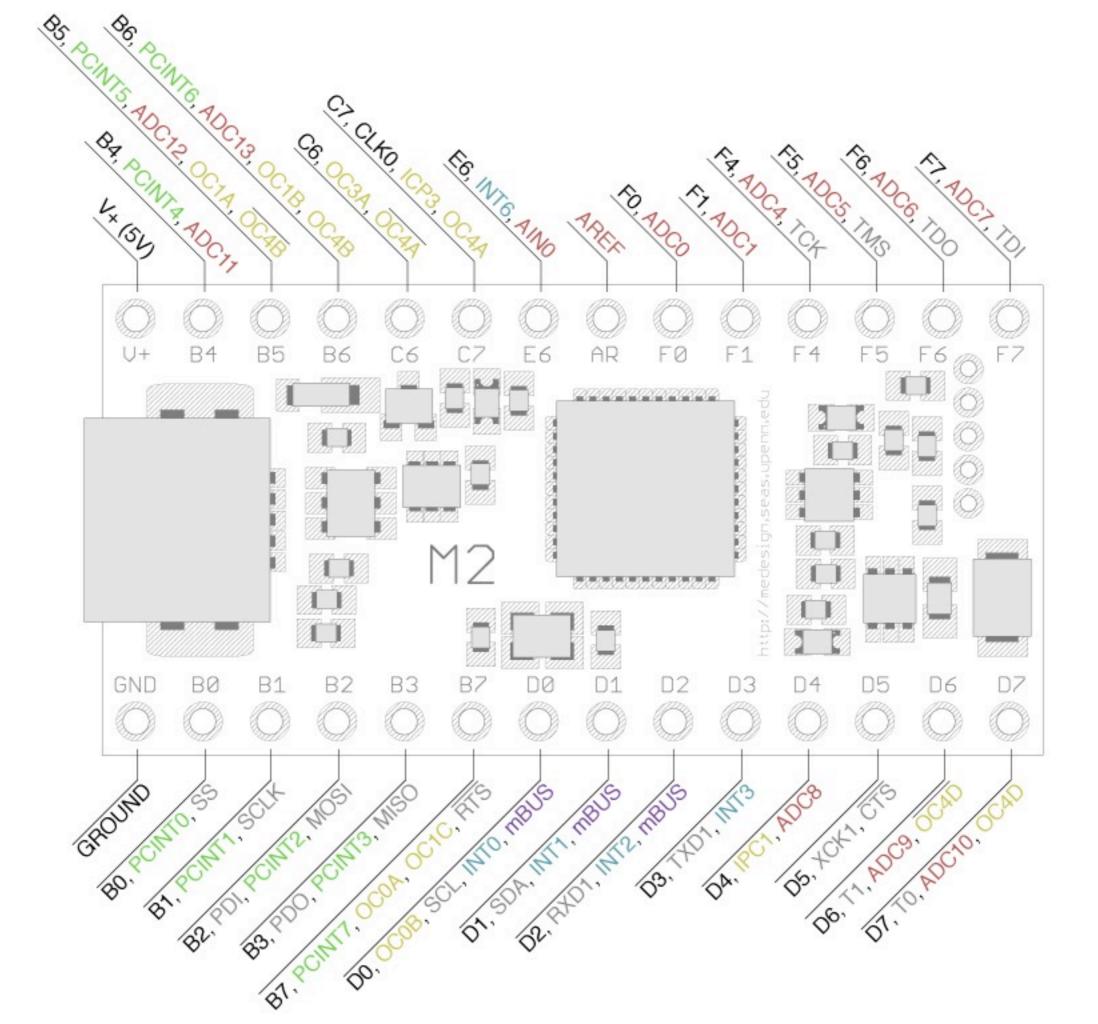

## ATmega32U4 ADC

10-bit

successive approximation

12 channels

up to 15 ksps

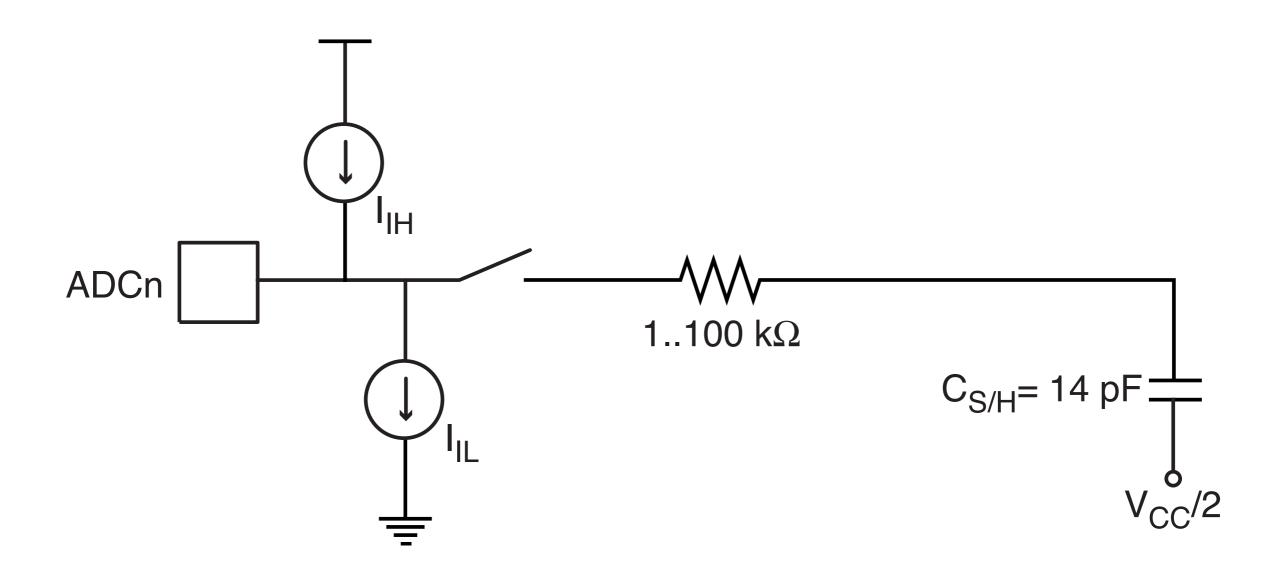

# **ADC**: inputs

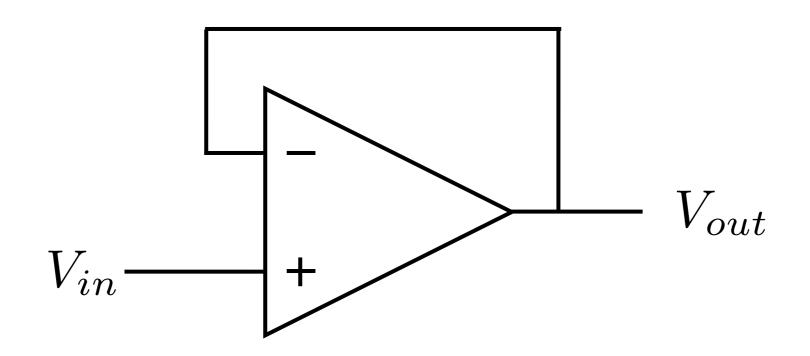

## ADC: inputs - buffering!

$$V_{out} = V_{in}$$

high-impedance input low-impedance output

## **ADC**: inputs

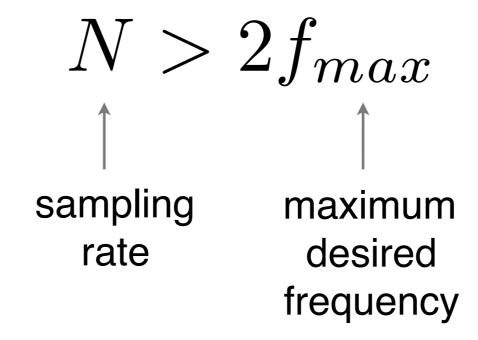

### **Anti-Aliasing & The Nyquist Theorem**

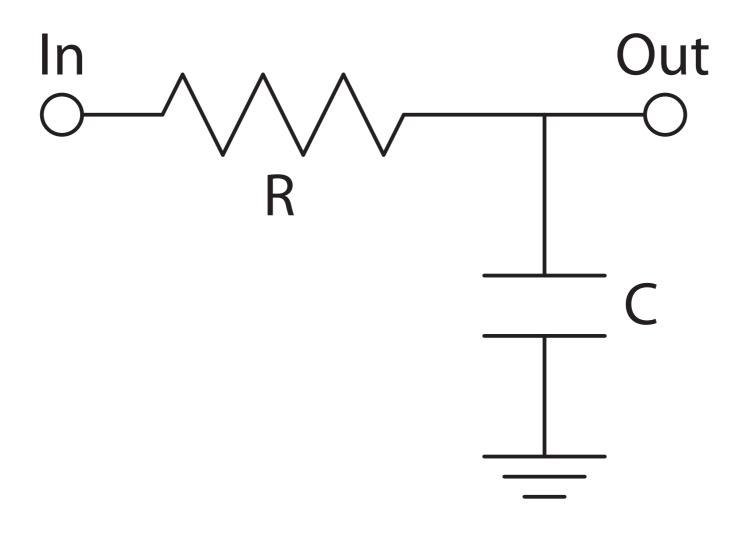

Add a buffered RC low-pass filter before the input to the microcontroller

recommended cutoff < 100 kHz

# ADC: inputs - filtering!

$$f_c = \frac{1}{2\pi RC}$$

## **ADC**: process

set the voltage reference

set the ADC clock prescaler

disable some digital inputs

set up interrupts and triggering, if desired

select the desired analog input

enable conversions

start the conversion process

read the result

## ADC: voltage reference

setting the MAX value (0x03FF) to one of the following:

external AREF (default!)

Vcc

2.56V

ADMUX: REFSI, REFS0

## ADC: prescaler

set ADC clock to 50-200kHz

driven from system clock

ADCSRA: ADPS2, ADPS1, ADPS0

## ADC: digital disable

turn off the digital input circuitry

DIDR0 :ADCnD (for n=0...7)

DIDR2:ADCnD (for n=8...13)

## **ADC**: triggering

single-conversion (leave alone)

VS.

free-running

**ADCSRA: ADATE**

## **ADC**: input selection

single ADC unit

12 multiplexed inputs

ADCSRA: MUX5

ADMUX: MUX2, MUX1, MUX0

### **ADC:** enable and start

must enable and start conversion

ADCSRA: ADEN ADCSRA: ADSC

## **ADC: results**

16-bit pseudoregister